阻抗,比较通俗地讲,就是在具有电阻、电感和电容的电路里,对电路中的电流起阻碍的作用叫做阻抗,以欧姆作为单位。

任何线路在通过一定的交流频率下,都会呈现出特定的阻抗,它会随着交流频率的增加而增加。我们常说的特征阻抗即是交流信号在传输过程中,在信号到达的某个点,传输线和参考平面之间会形成一个电场,同时会产生一个瞬间的小电流,这个小电流在传输线中的任何一个点都是存在的,传输线的每一点就会等效成一个电阻,这个电阻就被称为线路的特征阻抗。任何一根导线,在流经高频信号时,都会呈现出特定的电抗特性。

计算公式:Z= R+j (XL–XC)。其中R为电阻,XL为感抗,XC为容抗。如果( XL–XC) > 0,称为“感性负载”;反之,如果( XL–XC) < 0称为“容性负载”。电阻、电感的感抗、电容的容抗三种类型的复合物,统称“阻抗”。

为什么要阻抗匹配:

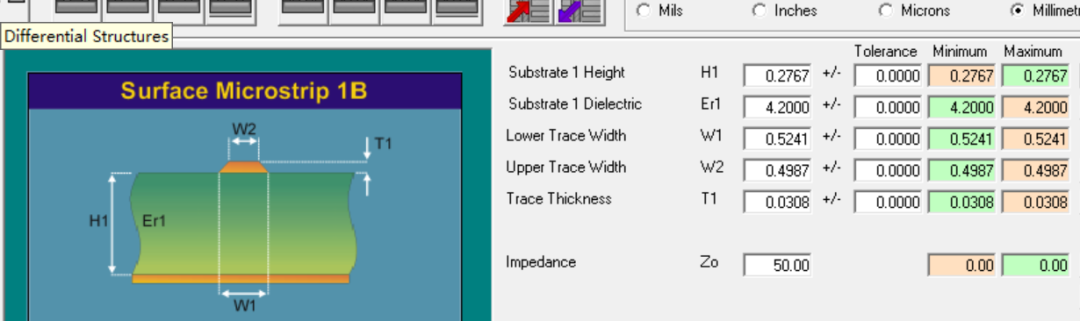

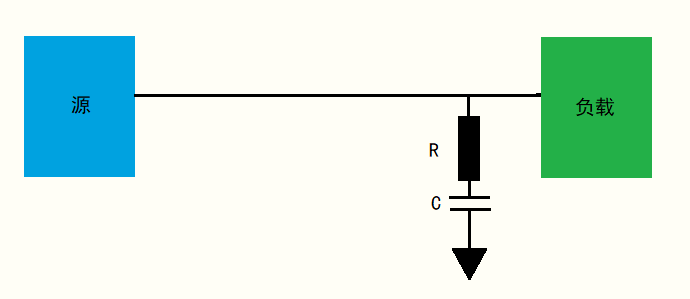

阻抗匹配就是为了信号能更好的传播。我们希望有用信号能够无衰减或者以最小衰减的方式传输到负载,如果阻抗不匹配的话,反映到系统上就是该器件的回波损耗差。这个反射回去的信号,会对系统造成很大的影响,甚至烧坏某些器件。对于EMC而言,这个被反射的信号,还会引起对外的电磁辐射,从而降低了电路的电磁兼容性能,严重时会直接影响到设备或系统的安全性。 下图是理想的阻抗匹配模型,以射频信号50欧姆为例,即源阻抗=传输阻抗=负载阻抗=50欧,在实际的工程应用中,这样的结论是不存在的,我们常说的阻抗匹配,只是通过电路设定,使源阻抗、传输阻抗、负载阻抗三者趋于理想的状态。

我们知道,阻抗匹配的两个基本条件:一是负载阻抗等于源内阻抗,即它们的模与辐角分别相等;二是负载阻抗等于信源内阻抗的共轭值,即它们的模相等而辐角之和为零。

要达到阻抗匹配,设计时可采用两种基本方法:一是改变阻抗力,改变阻抗力就是通过电容、电感与负载串、并联,来调整负载阻抗值,以达到源和负载阻抗之间的匹配;二是调整传输线,调整传输线是加长源和负载间的距离,配合电容和电感把阻抗力调整为零。此时信号不会发生反射,能量都能被负载吸收。

影响PCB阻抗的因素:

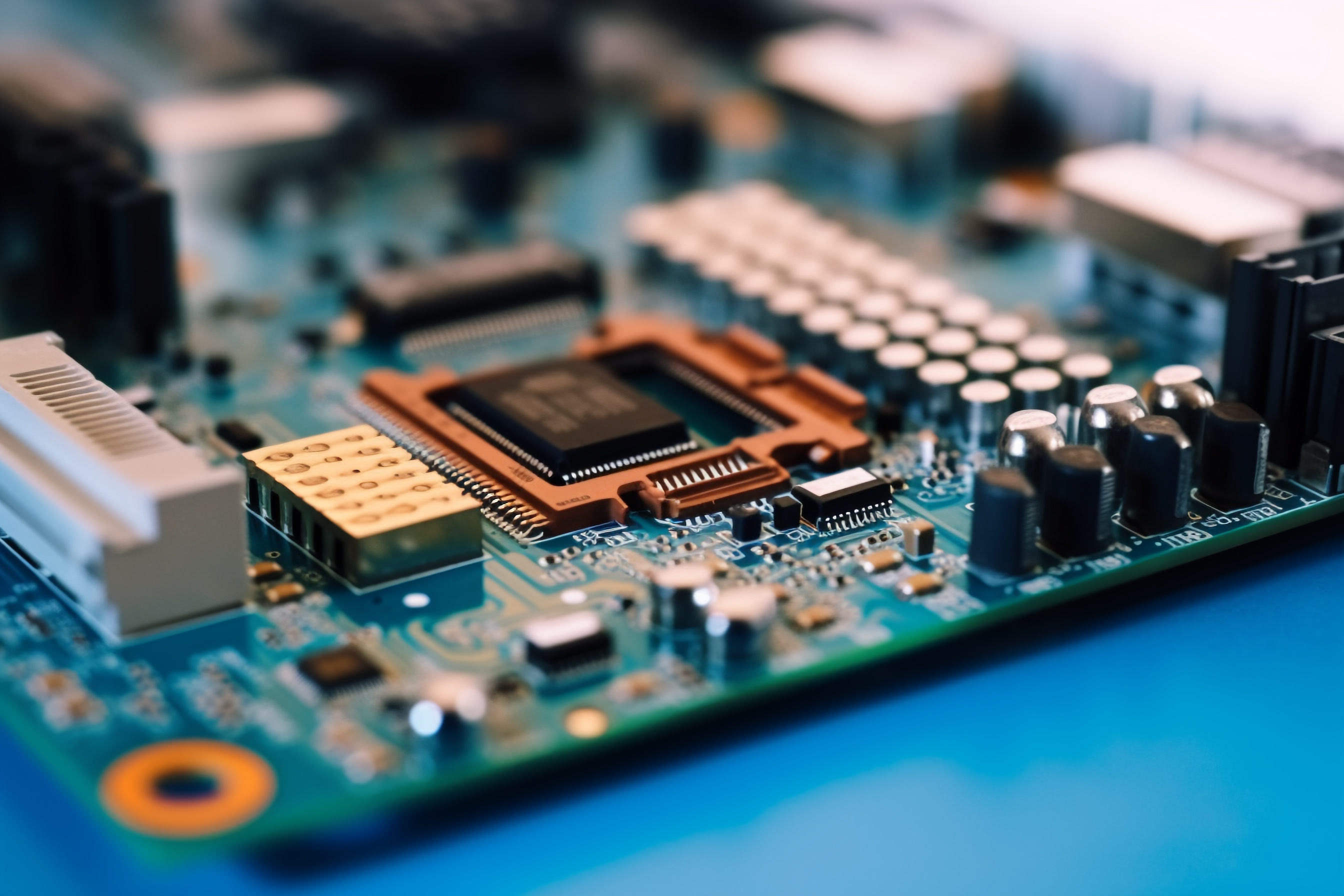

前面讲过两个基本条件和两个基本方法,可想而知,PCB的设计对于阻抗匹配起着至关重要的决定。高速PCB布线中,一般把数字信号的走线阻抗设计为50欧姆,差分信号线设计为90-100欧姆。高频领域中,信号频率对PCB走线的阻抗值影响非常大,同一线路或系统中,信号频率越高、呈现的阻抗越大,一般来说当数字信号边沿时间小于1ns或者模拟信号频率超过100M时就必须考虑阻抗问题。PCB走线的阻抗主要来自寄生的电容、电阻和电感系数,主要因素有材料介电常数、线宽、线厚乃至焊盘的厚度等。PCB阻抗的范围是25至120欧姆,如USB、LVDS、HDMI、SATA等,为了达到传输效率,降低电磁辐射,一般会做90-100欧姆阻抗控制。在PCB走线设计中,影响阻抗匹配的因素较多,主要有:

1)PCB板厚,板材的介质;

2)顶层走线宽度,铜厚度;

3)线间距,走线周围包地间距;

4)PCB走线的长度;

5)PCB过孔;

6)表面绿油厚度;

要实现阻抗匹配,需要使用TDR来进行测量,如果阻抗值没有进行仿真,我们仍然需要根据实际工程应用来进行调整。

差分线设计

差分线等长包地设计

对于宽度确定的PCB走线,有以下几个因素会影响到走线的阻抗。

首先是 PCB 走线和参考平面的高度,走线距参考平面越低,走线上的近场EMI可以被很好地吸收,也就是说PCB走线离参考平面的高度越低意味着辐射越小,EMC效果越好;其次,干扰会随走线高度发生明显的变化,把PCB走线的高度减少一半,干扰会减少到近四分之一;最后,介质高度的影响,走线确定的情况下,介质高度越低,其阻抗越小,不易受电容性负载影响,由于受PCB加工工艺的限制和芯片阻抗的设计要求,走线阻抗一般很少有低于50欧姆的要求,50欧姆也是射频领域通用的阻抗标准。

阻抗匹配的方式:

阻抗匹配的方法有很多,但在EMC调试整改的工程应用中,阻抗匹配的方法主要运用串联、并联和RC三种终端匹配方案。

1)串联终端匹配

串联终端匹配简单理解就是在源端与负载端增加一个合适电阻,使源端、传输线、负载端达到匹配的目的。优点是器件单一,只需要一个电阻元件,能抑制振铃,减少过冲,可以增强信号完整性,产生更小的EMI。

2)并联终端匹配

并联终端匹配是通过一个电阻R将传输线的末端(可能是开路,也可能是负载)接到地或者接到VCC上,电阻R的值必须同传输线的特征阻抗匹配,以消除信号的反射。优点是器件单一,只需要一个电阻元件,适用于分布式负载,反射几乎可以完全消除,电阻阻值易于选择。

3)RC终端匹配

RC终端匹配的优势在于终端匹配电容阻断了直流通路,因此节省了电路的功率消耗,同时恰当地选取匹配电容的值,可以确保负载端的信号波形接近理想的方波,同时信号的过冲与下冲又都很小。缺点是电容值非常难匹配,匹配不好时,不仅不能达到阻抗匹配的目的,反而因RC的时间常数不正确,形成一个尖峰发生器,引起信号过冲和辐射。

阻抗匹配整改案例分析:

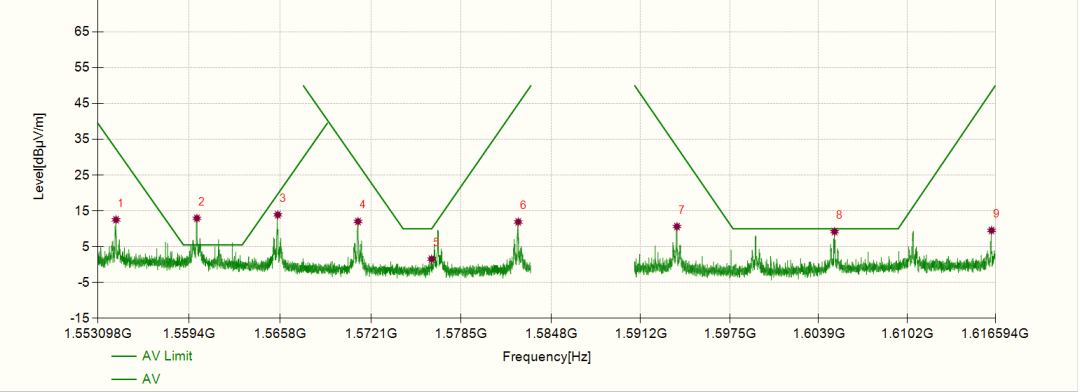

某车载显示系统,EMC试验过程中,辐射发射项目在导航频段超标,频谱图如下,分析数据后,从波形判断,该噪声呈一定的倍数关系,计算两频率点的间隔大致在5.6MHz左右,可能是某一频率的高次谐波信号,对于高频信号而言,频率越高,波长越短,辐射所需的天线长度就越短,接近1/4即可形成有效辐射。在电子电路中,模拟电路、开关电源等,其谐波能量很少能倍至GHz级别,只有高速信号或数字信号,才可能达到这个级别。

不合格数据

整改过程中,采用近场探头和频谱仪进行噪声跟踪定位,经排查确认,最大辐射区域为屏驱动芯片与显屏接口处。频谱仪曲线图如下图所示,频率点与扫描数据完全吻合,精准定位出电路的辐射源。

分析电路原理,屏信号采用的差分传输方式,差分信号的优点是抗干扰能力强,时序精准,能够精确识别小幅度信号,能够减少共模噪声信号。但是在PCB设计时,如果传输线路的阻抗失配,高频信号将会被反射号,对空间形成辐射。对于高速信号线,尤其是差分信号线的电磁辐射,首先要考虑是否是由于传输阻抗失配反射引起的辐射,通过前面对阻抗匹配的原理讲解和工程应用方法,最直接的方法就是改变传输线路中的匹配电阻从而改善EMI性能。由于在设计中,影响阻抗匹配的因素较多,理论参数与实际参数可能存在偏差,仍然要以工程调试结果为准。

通过不断地调试和验证,将差分信号的匹配电阻更换为90欧姆效果最好,经调整后再测试,高频谐波得到很好地抑制,最终测试通过。

合格数据

项目总结:

高速电路的传输信号必须考虑其阻抗匹配问题,只有实现了输出阻抗与负载阻抗“完美”的匹配,才能实现电磁波信号的无反射传输,改善EMI性能,如果传输线路中出现不匹配就会引起严重的信号反射,这不仅影响信号的传输效率、信号质量,还会影响产品的EMC性能,导致辐射测试不通过,在电路的前期设计不充分的情况下,需要反复的整改调试,不仅延长了产品检测周期,还增加了认证检测的成本。只有在PCB设计之初,将阻抗匹配的各种不利因素考虑在其内,即便在EMC检测过程中出现问题,也能精准定位故障,快速调试参数,解决各种信号干扰问题,最终顺利通过产品的认证检测。

广州顺泰在EMC测试、认证服务方面,拥有专业的技术专家团队,可一对一帮助客户解答和攻克EMC设计难关,能够为乘用汽车、各类电动车、摩托车及其电子部件产品提供专业、高效的电磁兼容解决方案。

最新资讯

![]() AIS认证(或汽车行业标准)是印度政府1989年颁布的中央机动车辆法规Central Motor VehiclesRules(简称CMVR)的一部分,该法规中的第126条对所谓的型式认可进行了定义。

AIS认证(或汽车行业标准)是印度政府1989年颁布的中央机动车辆法规Central Motor VehiclesRules(简称CMVR)的一部分,该法规中的第126条对所谓的型式认可进行了定义。![]()

顺泰技术解析 | EMC传导骚扰电流法与电压法之差异

广州顺泰在EMC测试、认证服务方面,拥有专业的技术专家团队,可一对一帮助客户解答和攻克EMC设计难关,能够为乘用汽车、各类电动车、摩托车及其电子部件产品提供专业、高效的电磁兼容解决方案。![]()

顺泰认证分享 | 西班牙V16 (DGT 3.0带GPS通信方案) 认证

广州顺泰可提供紧急信号装置V16完整测试&认证服务,并为客户提供V16 (DGT 3.0带GPS通信方案) 认证指导方案。![]()

顺泰技术分享 | 汽车电子后视镜CMS灰度等级复现测试

广州顺泰投建华南首家电子后视镜CMS影像自动化实验室,可满足GB 15084、QCT/1128到ISO 16505、ECE R46等国内外标准法规测试要求。![]()

SQT资讯| 顺泰实验室获印度ICAT授权,助力知名整车厂商取得印度证书

顺泰实验室顺利通过了各项严格考核与评定,获得了ICAT目击实验室认可。![]()

顺泰认证分享 | 回复反射器UN R150欧盟认证

在Emark认证方面,顺泰拥有回复反射装置一站式检测、认证服务能力,是欧盟发证机构授权和直接合作单位,能够为客户申请多家交通部颁发的R150 E-mark证书。![]()

顺泰技术解析 | EMC电磁环境背景小知识

顺泰公司拥有3套半电波暗室测试系统,均可用于发射类试验项目和抗扰类试验项目的测试需求。![]()

顺泰认证分享| 机动车照明与信号装置欧盟认证

顺泰拥有机动车灯具一站式检测、认证服务能力,是欧盟发证机构授权和直接合作单位,能够为客户申请多家交通部颁发的R148/R149 E-mark证书。![]()

顺泰技术分享 | 汽车电子后视镜CMS模拟点光源测试

广州顺泰在传统后视镜测试能力上拓展了电子后视镜的测试能力,能够提供CMS一站式解决方案,涵盖电子后视镜系统测试、电磁兼容测试、环境可靠性测试、ECE R46 Emark认证等。![]()

广州顺泰智能驾舱-CMS影像自动化实验室

汽车电子智能化浪潮的不断推进,加速越来越多的车企,通过配置或升级智能驾舱系统,来提升整车个性化智能驾驶体验,车载相机、显示屏、摄像监控系统(CMS)、HUD等图像系统在汽车平台上的应用快速增长。![]()

顺泰认证分享| 警示灯ECE R65认证解析

广州顺泰拥有独立的光学实验室,可提供警示灯ECE R65一站式专业、高效的测试、认证服务。![]()

GB15084-2022-CMS图像质量测试前提-CMS测试相关参数简介

常规的电子产品测试可能只需提供电压和接线方式就可进行测试,但CMS送样测试并不像大家想象的那么简单,CMS测试不是单单提供一套系统就可进行测试,还需提供以下表格的相应参数,才可进行测试。![]()

顺泰技术解析 | 阻抗匹配在EMC中的重要性

广州顺泰在EMC测试、认证服务方面,拥有专业的技术专家团队,可一对一帮助客户解答和攻克EMC设计难关,能够为乘用汽车、各类电动车、摩托车及其电子部件产品提供专业、高效的电磁兼容解决方案。![]()

GB15084-2022-CMS检测项目法规要求及测试方法介绍

广州顺泰在传统后视镜的测试、认证能力上拓展了电子后视镜的测试、认证能力,能够为客户提供电子后视镜E-mark认证及GB15084-2022整套标准测试服务。![]()

顺泰技术解析 | 浅谈电容在 EMC 整改中的运用

广州顺泰在EMC测试、认证服务方面,拥有专业的技术专家团队,可一对一帮助客户解答和攻克EMC设计难关,能够为乘用汽车、各类电动车、摩托车及其电子部件产品提供专业、高效的电磁兼容解决方案。![]()

顺泰技术解析 | 车灯大电流注入(BCI)整改案例

对于BCI大电流试验失效的整改,工程师需要了解其干扰机理,定位其干扰路径、分析其受扰电路或模块,才是解决问题的关键。屏蔽、接地、旁路、去耦、阻抗调整、数字滤波等都是解决电磁干扰的有效手段。![]()

广州顺泰环境可靠性测试实验室

广州顺泰环境可靠性实验室,可全方位满足整车及零部件供应商国内、国际、欧标、美标及企业标准等测试认证需求。![]()

顺泰技术解析 | CAN通信辐射骚扰设计整改案例

广州顺泰在EMC测试、认证服务方面,拥有专业的技术专家团队,可一对一帮助客户解答和攻克EMC设计难关,能够为乘用汽车、各类电动车、摩托车及其电子部件产品提供专业、高效的电磁兼容解决方案。![]()

顺泰技术解析 | 汽车仪表总成静电整改案例分享

广州顺泰在EMC测试、认证服务方面,拥有专业的技术专家团队,可一对一帮助客户解答和攻克EMC设计难关,能够为乘用汽车、各类电动车、摩托车及其电子部件产品提供专业、高效的电磁兼容解决方案。![]()

广州顺泰车灯光学实验室

光学暗室测试能力可满足包括GB国标、ECE欧标、ISO国际标准、ADR澳大利亚法规、FMVSS 108及SAE美标等在内的全球主要国家及其地区机动车光学标准法规。